## Frequency Translation MMICs Using InP HEMT Technology

Long Tran, Michael Delaney, Russ Isobe, Derek Jang, Julia Brown\*

Hughes Space and Communications Company, El Segundo, California

\*Hughes Research Laboratory, Malibu, California

### ABSTRACT

Frequency translation circuits are key elements in communication systems. This paper presents three different frequency multipliers and a frequency mixer designed using the InP HEMT technology. These successful first iteration MMICs are highlighted by a V-band frequency quadrupler that has 14.25 dB conversion gain with +3.25 dBm output power and a V-band mixer that has 10dB conversion loss over a 12 GHz bandwidth.

### INTRODUCTION

It has been shown that InP HEMT is the device of choice for low noise, high frequency applications. With the device noise figure of around 1 dB at 60 GHz and greater than 300 GHz cutoff frequency [1], this technology is an ideal process for the development of millimeter-wave low noise amplifiers [2]. The utility of this device does not end at low noise applications, however. Similar to its relative, the GaAs MESFET, the InP HEMT can be used in many other applications including frequency conversions. Since the device has a low pinch-off voltage, high gain, and high cut-off frequency, multipliers using this device require significantly lower input power level while still achieving excellent conversion gain at Q-band and above. Similarly, mixers require much lower LO drive to perform their functions. In this first iteration, we have successfully developed frequency multipliers that operate at Ka-band and V-band as well as a frequency downconverter that operates at V-band. This paper discuss the InP HEMT structure, the design software, followed by a discussion of the MMIC designs and test results.

### InP HEMT STRUCTURE

Lattice-matched to a 3-inch InP semi-insulating substrate, the InP HEMT structure consists of a

250 nm undoped AlInAs buffer with a 40 nm GaInAs channel, a 1.5 nm undoped spacer, an 8 nm AlInAs donor layer, and a 7 nm GaInAs doped cap. The electron sheet density is around  $2.7 \times 10^{12} \text{ cm}^{-2}$  and the electron mobility is between 10,000 to 11,000  $\text{cm}^2/\text{Vs}$  at 25°C. A double-exposure e-beam lithography process is used to create a highly repeatable 0.1  $\mu\text{m}$  gate definition through the resist [1]. To shield the active device from moisture and contamination, a 100 nm thick silicon nitride passivation layer is used.

Figure 1. Layout of the Ka-band MMIC frequency doubler.

### DESIGN SOFTWARE AND MODELING

All circuit-level simulations and layouts were done using HP-EEsof's Academy/Libra™. Microstrip discontinuities such as tee-junctions and cross-junctions were analyzed using Sonnet em™. Walter Curtice's FETFIT™ software was used to generate the HEMT large-signal model.

### MMIC DESIGNS AND TEST RESULTS

#### Ka-BAND FREQUENCY DOUBLER

A 150  $\mu\text{m}$  x 0.1  $\mu\text{m}$  HEMT, biased at 1.5V at the drain and pinched off, is used to perform the frequency multiplication. When an AC voltage, applied to the gate of the device, varies between turn-off and 0V, it causes the device to generate a

TU

4A

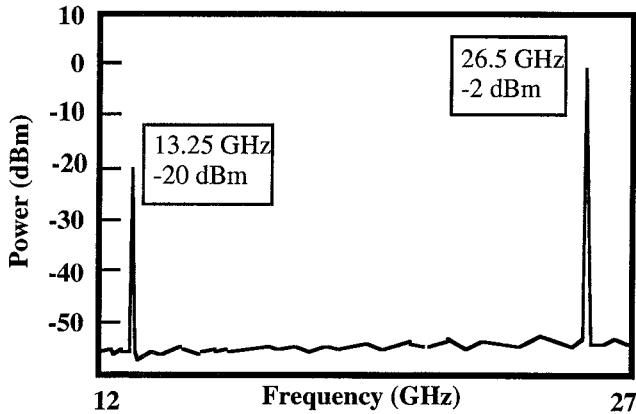

drain current rich in harmonics. A quarter-wave open stub is placed at the drain to reject the fundamental and third harmonic while passing the desired second harmonic with minimal loss. A matching network is also placed at the output to provide the appropriate load to optimize second harmonic power. An amplifier using a single 50  $\mu\text{m} \times 0.1 \mu\text{m}$  HEMT precedes the multiplier and provides the proper drive level at the fundamental frequency (see Figure 1). Dissipating 27 mW of DC power, this amplifier/doubler generates a 26.5 GHz signal at -2 dBm when a 13.25 GHz signal at -7.5 dBm is applied to the input (see Figure 1a). The fundamental rejection is better than 16 dBc.

Figure 1a. Output response of the Ka-band MMIC frequency doubler.

### V-BAND FREQUENCY DOUBLER

Like the Ka-band doubler, the harmonics generator is a 150  $\mu\text{m} \times 0.1 \mu\text{m}$  device biased at 1.5V and pinched off. The resonator and the output matching network are designed to provide optimum load match for the second harmonic and to reject the fundamental as well as the third

Figure 2. Layout of the V-band MMIC frequency doubler.

|                    | Simulation | Measured |

|--------------------|------------|----------|

| Input Freq (GHz)   | 27         | 27       |

| Input Power (dBm)  | 0          | 0        |

| Output Freq (GHz)  | 54         | 54       |

| Output Power (dBm) | 6          | 5        |

| Fundamental (dBm)  | -10        | -11      |

Table 1. Output response of the V-band MMIC frequency doubler.

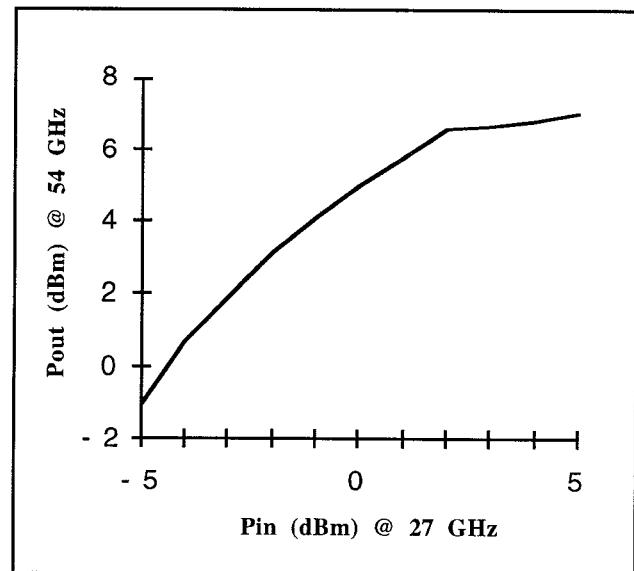

Figure 2a. Pout vs. Pin for the V-band MMIC frequency doubler.

harmonic. The second harmonic signal is then fed to an output amplifier to increase the output power to about 5 dBm. The MMIC is 1.5 mm  $\times$  2.5 mm in size and consumes 55 mW of DC power (see Figure 2). Test measurements show that a 27 GHz signal at 0 dBm applied to the input generated a 54 GHz second harmonic at 5 dBm with the fundamental signal rejection of greater than 15 dBc (see Table 1). Test results also show that this MMIC is capable of generating 7 dBm of output power (see Figure 2a).

### V-BAND FREQUENCY QUADRUPLER

This MMIC combines the Ka-band doubler and the V-band doubler discussed previously. Occupying an area of 1.5  $\times$  4 mm, this four stage circuit uses a 50  $\mu\text{m}$  device for the Ku-band driver amplifier, a 150  $\mu\text{m}$  device for the Ka-band doubler, a 150  $\mu\text{m}$  device for the V-band doubler, and a 150  $\mu\text{m}$  device for the output amplifier (see Figure 3). Test results show that a 13.5 GHz

signal at -11 dBm applied at the input generated a 54 GHz fourth harmonic signal at +3.5 dBm.

Figure 3. Layout of the V-band MMIC frequency quadrupler.

|                    | Simulation | Measured |

|--------------------|------------|----------|

| Input Freq (GHz)   | 13.5       | 13.5     |

| Input Power (dBm)  | -11        | -11      |

| Output Freq (GHz)  | 54         | 54       |

| Output Power (dBm) | 4          | 3.25     |

| 5th Harmonic (dBc) | -34        | -35      |

Table 2. Output response of the V-band MMIC frequency quadrupler.

The fifth harmonic rejection was about 35 dBc (see Table 2). The DC power dissipation for the tested frequency quadrupler was 72 mW.

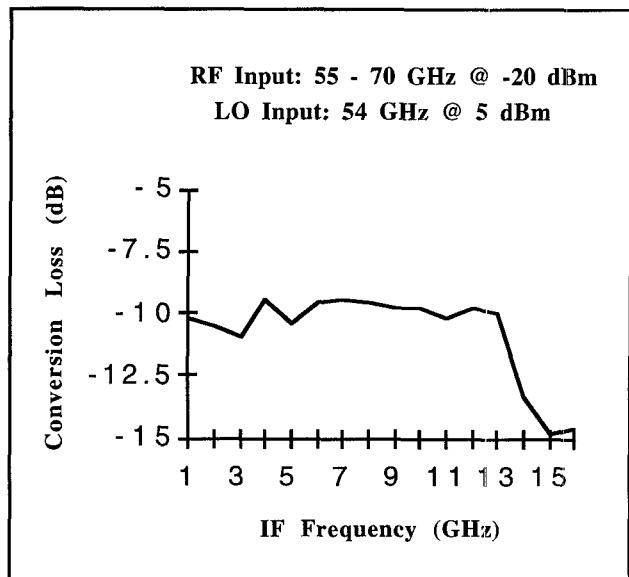

## V- BAND FREQUENCY MIXER

This circuit was designed to perform frequency downconversion using a 100  $\mu$ m x 0.1  $\mu$ m HEMT (see Figure 4). Passive FET frequency mixing technique was chosen to eliminate many possible problem causing intermodulation products. The disadvantage of this technique is that there is always conversion loss (>6 dB). An LO signal is used to modulate the gate which in turn causes the drain resistance to vary nonlinearly at the LO frequency. An RF

Figure 4a. Output response of the V-band MMIC mixer.

signal is then injected into the unbiased drain and the result is an array of mixing products one of which is the IF signal ( $f_{if} = f_{rf} - f_{lo}$ ). The LO matching circuit is a band-pass filter that matches the gate of the device to 50 $\Omega$  at the LO frequency. The RF matching circuit is a bandpass filter matching the drain of the HEMT to 50 $\Omega$  at the RF frequency while presenting a high impedance at the IF frequency. Since the RF and IF frequency are far apart (RF at V-band and IF at X-band), a small series capacitor placed at the point where the RF matching circuit interfaces with the drain and the IF port was sufficient in rejecting the IF signal. Quarter-wave line, radial stubs, microstrip lines and MIM capacitors were used as part of the output matching circuit designed to pass the IF signal from the device to 50 $\Omega$  with minimal loss and to prevent any RF signal from leaking through. When a 54 GHz signal at 5 dBm is applied to the LO port and the RF port is swept from 55 GHz to 70 GHz at -20 dBm, the downconverted IF signal showed around 10 dB conversion loss over a 12 GHz bandwidth (see Figure 4a).

## SUMMARY

Two frequency doublers, a frequency quadrupler, and a mixer were developed in the InP HEMT technology. The 54 GHz frequency quadrupler achieved over 14 dB conversion gain while generating more than 3 dBm output power.

Figure 4. Layout of the V-band MMIC mixer.

Both the K-band and the V-band doublers have over 5 dB conversion gain and provided -2 dBm and 5 dBm of output power, respectively. The V-band frequency downconverter was designed and proven to have over 12 GHz bandwidth with 10 dB average conversion loss.

#### **ACKNOWLEDGMENTS**

We would like to thank Christine Lennon and Randy Sakamoto for their guidance in this InP HEMT MMIC developmental work. We would also like to thank Mark Bezaire, Melissa Melendes and Renee Quen Wong for their support.

#### **REFERENCES**

- [1] L. Nguyen, et al; 1993 IEEE MTT-S Digest

pp 345-7

- [2] R. Isobe, et al; 1995 IEEE MTT-S Digest

pp 1133-6